1

定论

I/O系统基本概念

- 考纲已删除

I/O接口

- 定义 - 主机与外设之间的交接界面

- 功能

- 地址译码与设备选择

- 实现主机与外设之间的联络通信联络控制

- 实现数据缓冲

- 信号格式的转换

- 传送控制命令和状态信息

- I/O接口的通用结构

- 数据线传输读写数据、状态信息和控制信号等

- 控制线传输读/写控制信号

- 地址线传送访问I/O接口中寄存器的地址

- I/O接口的分类

- 数据传送方式 - 并行接口、串行接口

- 主机访问I/O设备的控制方式 - 程序查询接口、中断接口、DMA接口

- 功能选的的灵活性 - 可编程接口和不可编程接口

- I/O端口

- 定义 - I/O接口中可被CPU直接访问的寄存器

- 分类 - 数据端口、状态端口(只有读操作)和控制端口(只有写操作)

- 独立编址(I/O映射方式)

- 对所有I/O端口单独编址,I/O端口地址空间与主存地址空间相互独立。因此他们的范围可以重叠

- 因此需设定专门的I/O指令来说明访问的是I/O空间,I/O指令的地址码给出I/O端口号

- 优点是地址线少,I/O译码更简单、寻址速度更快

- 缺点是程序设计灵活性差,需提供两组控制信号增大控制复杂性

- 统一编址(存储器映射方式)

- 主存地址空间分一部分给I/O端口进行编址,I/O端口地址空间与主存地址空间共享同一地址空间,在不同段

- 因此需通过I/O指令的地址码来判断访问的是主存还是I/O端口,无需设置专门的I/O指令

- 优点是程序设计灵活性好,端口有较大的编址空间

- 缺点是地址线多,I/O译码更复杂、且部分主存空间被占用

I/O方式

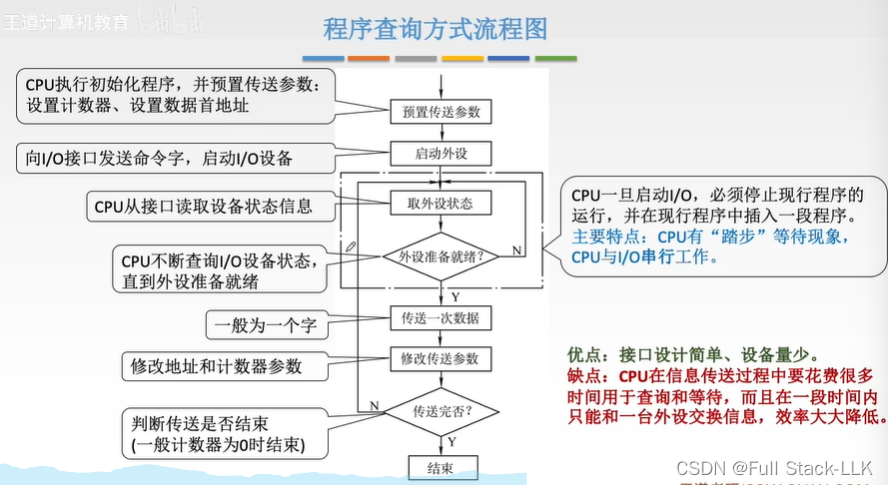

- 程序查询方式

- 图示

- 两种查询

- 独占查询 - CPU持续查询接口状态,花费100%时间用于I/O操作,外设与CPU串行工作

- 定时查询 - 周期性查询接口状态。条件满足后才进行一个数据的传输

- 图示

- 程序中断方式

- 定义 - 计算机执行程序的过程中,出现某些紧急情况或特殊情况,CPU停下当前程序转而去处理,处理完毕后再返回原程序断点处

- 示意图

- 程序中断方式的特点与设计思想

- 程序中断效率相关计算

- 程序中断的工作流程

- 中断请求 - 中断源是请求CPU中断的设备或事件,中断系统对每个中断源设置中断请求标志触发器。这些触发器可组成寄存器(集中在CPU或分散在各个中断源)

- 中断响应判优 - 是指CPU响应中断请求的先后顺序。一般来说DMA请求中断大于I/O请求中断

- CPU响应中断的条件 - 中断源有中断请求、CPU允许中断及开中断(异常和不可屏蔽中断不受此限制)、一条指令执行完毕(异常和不受此限制)

- 中断响应过程(由硬件实现)

- 关中断

- 保存断点至特定的寄存器与栈中

- 引出中断服务程序。识别中断源并将对应程序入口放入PC,有两种识别方式硬件向量法和软件查询法

- 中断处理过程

- 关中断

- 保存断点

- 中断服务程序寻址

- 保存现场和屏蔽字

- 开中断

- 执行中断服务程序

- 关中断

- 恢复现场和屏蔽字

- 开中断、中断返回

- 其中1-3由中断隐指令(硬件自动)完成,其余由中断服务程序完成

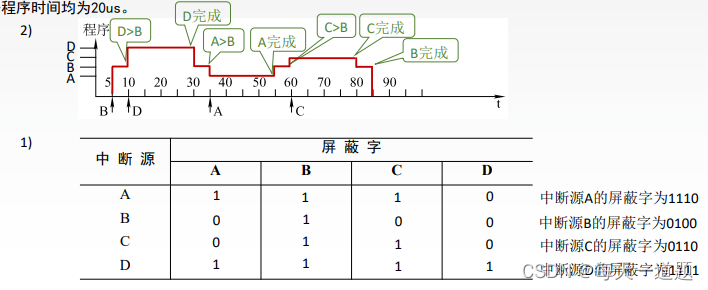

- 多重中断和中断屏蔽技术

- 单重中断即对优先级更高的中断请求不予响应,而多重中断则与之相反

- 多重中断的条件 - 中断程序中提前设置开中断指令,且优先级别高的中断源有权切断优先级别低的中断源

- 实现方式为每个中断源设置一个屏蔽触发器,1表示屏蔽该中断源的请求,所有屏蔽触发器组合在一起形成屏蔽字寄存器,屏蔽字寄存器内容为屏蔽字

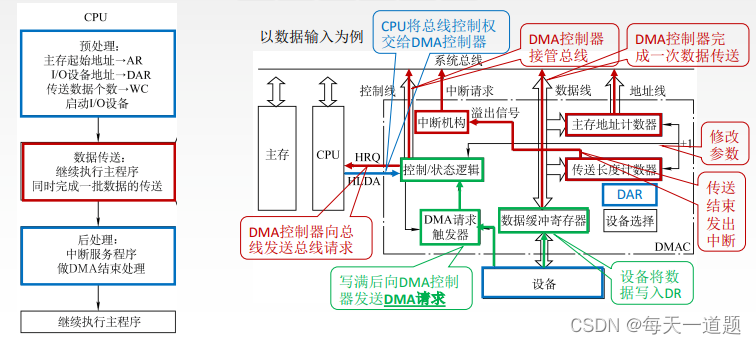

- DMA方式

- 定义 - 完全由硬件实现的成组信息传送的控制方式,在外设和CPU之间开辟一条直接信息通路

- DMA控制器的组成 -

对数据传送过程进行控制的硬件被称为DMA控制器(DMA接口)

- DMA的传送方式

- 停止CPU访存 - DMA接口向CPU发送一个停止信号,使CPU放弃总线控制权,停止访问主存,直到DMA传送完成

- 周期挪用 - 通过临时借用 CPU

的总线周期完成数据传输。其核心机制是:DMA 控制器在需要传输数据时,暂停

CPU

对总线的使用权,挪用一个或多个总线周期进行数据搬运,完成后立即归还总线控制权,让

CPU 继续执行原任务。

场景 1:CPU 不访问内存 若 CPU 正在执行无需访存的指令(如乘法运算),DMA 可直接挪用总线周期,不影响 CPU 工作。

场景 2:CPU 正在访存 DMA 需等待当前 CPU 访存周期结束后,才能挪用下一个周期。

场景 3:访存冲突

若 CPU 和 DMA 同时请求访存,DMA 优先级更高(因外设数据可能丢失),此时 CPU 需延迟一个周期再访存。 - 交替访存 - 将CPU工作周期分为两个时间片。一个给CPU访存,一个给DMA访存、这种适合CPU工作周期比主存存取周期更长的情况

- DMA的传送过程

区别总结

| 对比维度 | 中断方式(Interrupt) | DMA方式(Direct Memory Access) |

|---|---|---|

| 数据传输路径 | 外设 → CPU → 内存(需CPU中转数据) | 外设 → DMA控制器 → 内存(无需CPU中转) |

| CPU参与度 | 全程参与:需执行中断服务程序完成数据读写 | 仅初始化和结束参与:初始化传输参数,结束时处理中断 |

| 传输效率 | 低:CPU需暂停当前任务,处理中断和数据传输 | 高:DMA直接控制总线,CPU可并行执行其他任务 |

| 适用场景 | 少量、非连续数据传输(如键盘、鼠标、串口通信) | 大量、连续数据传输(如硬盘读写、显卡数据传输) |

| 响应时间 | 较长:需保存CPU现场、跳转中断服务程序 | 较短:仅总线申请和释放时有短暂延迟 |

| 硬件复杂度 | 低:仅需中断控制器(如8259A) | 高:需专用DMA控制器(如8237)及总线仲裁逻辑 |

| 对CPU执行的影响 | 会打断CPU当前任务,存在上下文切换开销 | 仅在挪用总线周期时短暂影响,几乎不打断CPU执行 |

| 传输单位 | 通常按字节或少量数据块传输 | 可按块、页等大单位连续传输 |

从数据传送来看,中断方式靠程序,DMA方式靠硬件